随着物联网、人工智能、自驾车、高速运算、智能城市、5G等对异质整合封装需求增多,半导体制程的线宽线距越来越小,传统封装已无法因应,不同功能的芯片异质整合封装在一起将取而代之,面板级扇出型封装成为异质型封装的市场主流。研调机构Yole预估,全球先进封装市场规模将由2022年的443亿美元,成长为2028年的786亿美元,合计2022~2028年市场规模年复合成长率(CAGR)为10.6%。因应IC载板与车用半导体的缺料与产能供不应求的现象,扇出型封装技术更趋成熟,提供具有更高I/O密度的更大芯片,大幅减少系统尺寸,成为应对异构整合挑战的不二之选。

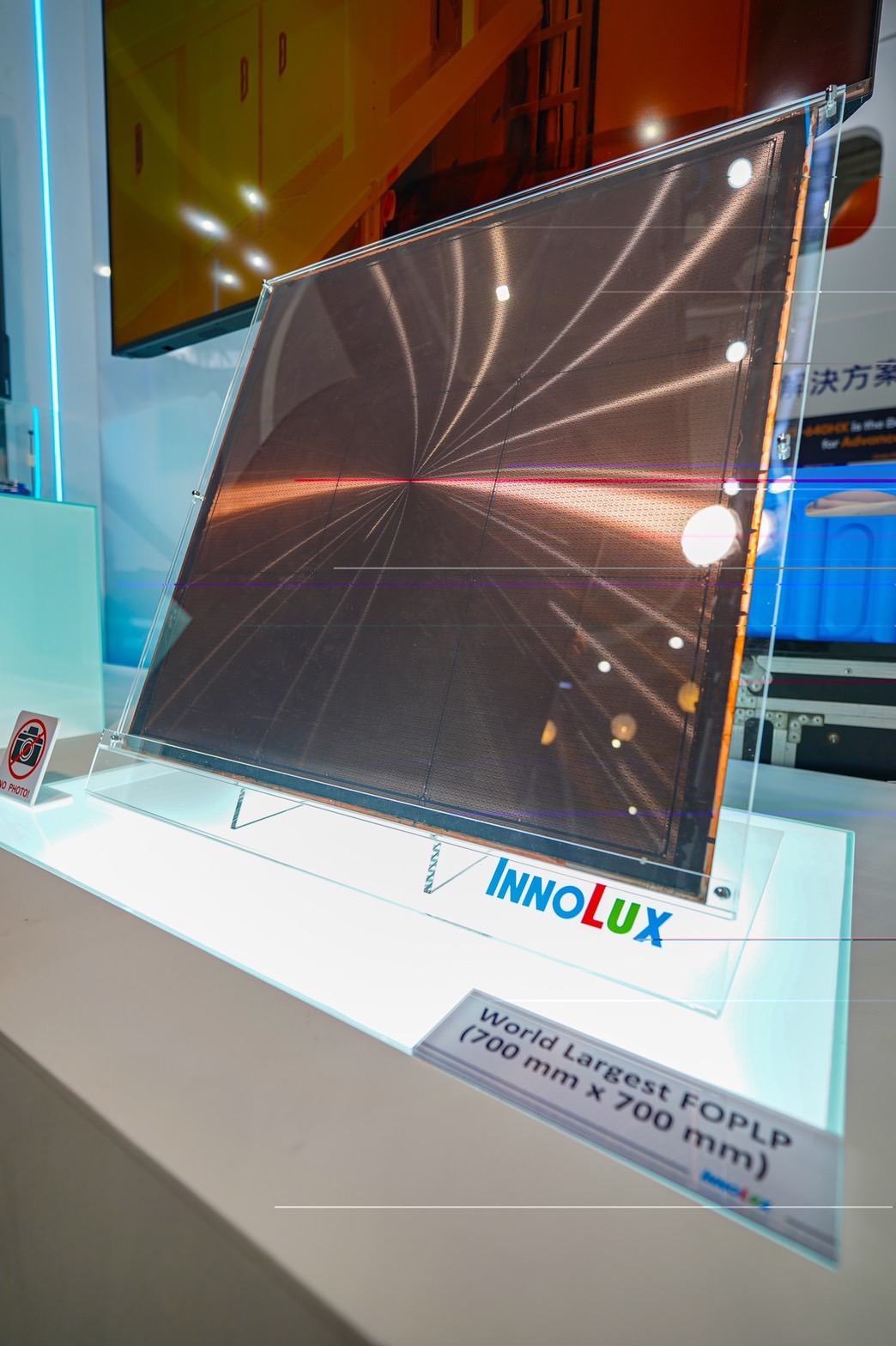

在经济部技术处A+计划支持下,群创光电以面板产线进行IC封装,得利于方形面积,相较于晶圆的圆形有更高的利用率,达到95%。以业界最大尺寸G3.5 FOPLP玻璃基板开发具备细线宽的中高阶半导体封装,面积是300mm玻璃晶圆的7倍。工研院协助群创光电克服减少面板翘曲量,让封装制程的破片与耗损更低,可「容纳更多的 I/O 数」、「体积更小」、「效能更强大」、「节省电力消耗」等技术优势,经济部技术处邱求慧处长表示,旧世代面板厂创新价值,群创产线正好补足半导体封装的缺口。看好面板级扇出型封装将是异质型封装的市场主流,群创指出,面板级扇出型封装可降低封装厚度、增加导线密度、提升产品电性,群创独家TFT制程技术,有效补足晶圆厂与印刷电路板厂之间的导线层技术差距。群创在台南3.5代厂打造RDL-first 以及Chip-first封装工艺,未来产能可达15K/月。

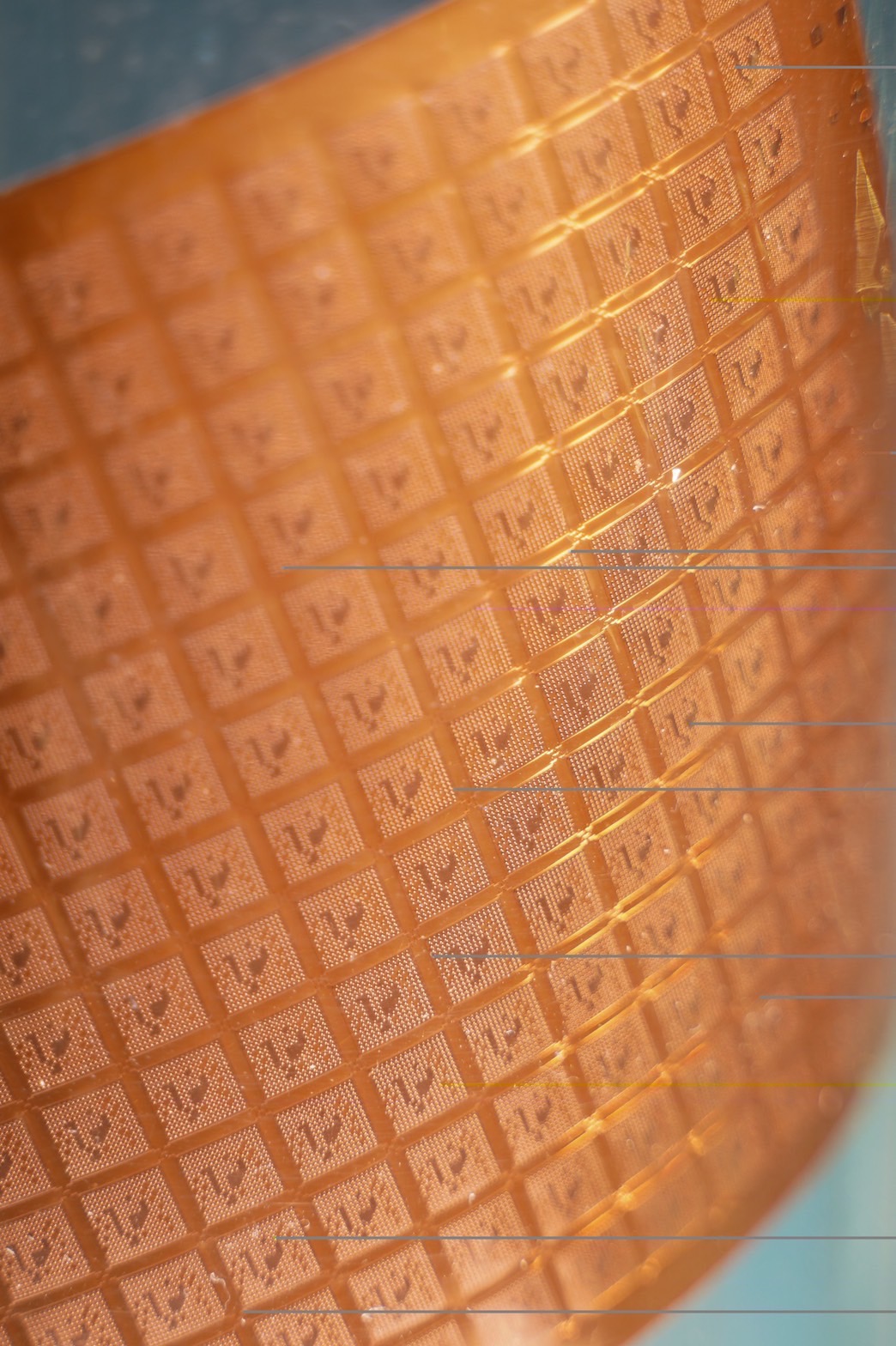

其中,群创chip-first工艺以金属基板开发芯片封装技术,使用WMF作为芯片绝缘层材料,可以轮刀进行芯片切割而不伤芯片,免除使用昂贵的雷射切割设备;厚铜重新布线(RDL)线路直接连接芯片(die)焊垫(bond pad),可满足高功率IC对线路低阻抗值的要求;此外具备6面保护(EMC)的封装结构,更可增强结构机械强度,提高芯片的信赖性,增强芯片对外界环境湿度的抵抗能力,可以通过潮湿敏感等级(MSL)1条件,特别适合要求可靠度、高功率输出之车用、功率芯片封装产品,目前已陆续送样,明年底可望量产。在高密度重布线层(RDL-first)工艺制程部分,以群创620x750mm为基板尺寸,制作高质量的精细线路,适用中高阶芯片封装,产线建置中。

群创具备大型面板尺寸的细线路制程经验与能力,可以快速切入封装RDL制程:此外,群创以最小世代TFT厂华丽转身为全球最大尺寸FOPLP厂,沿用70%以上TFT设备,已折旧完毕,成本最具竞争力。群创建构面板级封装制程之结构应力仿真平台,配合材料与制程参数之设计,以克服大面积基板导线层制程之翘曲问题;并建立整合薄膜组件之多功能导线层电路仿真设计能量与制程技术,取代原本由表面贴合组件组合之电路,减少使用组件之数量且微缩封装系统尺寸,以差异化设计扩大面板级导线层之竞争力与应用范畴。群创同时与策略伙伴合作开发全球最大基板尺寸之高均匀电镀设备与制程技术,以3.5代产线,达成低翘曲/高解析之面板级导线层技术,实现全球第一条面板产线转型封装应用,业界首创。

群创跨足半导体先进封装,加入IC design house、OSAT’s、IDM、Foundry及系统厂等半导体先进封装产业链,微小化芯片让生活更智能,更丰富。

群创RDL film

群创光电全球最大尺寸FOPLP 700X700mm

(1)(1).jpg)

(1)(1).jpg)